Pôvodne som chcel niečo jednoduché ako PMI-80 ale z 6502 Ale všetko čo som našiel používa dnes už nevyrábané IO a ich dnešná dostupnosť a cena je mimo môj rozpočet.

Aktuálne sa vyrábajú z rady 6502 okrem CPU a MCU len IO obvody PIA/65c21 VIA/65c22 ACIA/65c51. Preto som sa rozhodol pre návrh ktorý bude využívať len tieto obvody a celé riešenie nebude použivať IO obvody z iných CPU systémov. Preto som si nepostavil niečo od Granta 1 2. Ale upravil som návrh Garth Wilson-a. Menej ROM viac RAM a iné rozloženie IO.

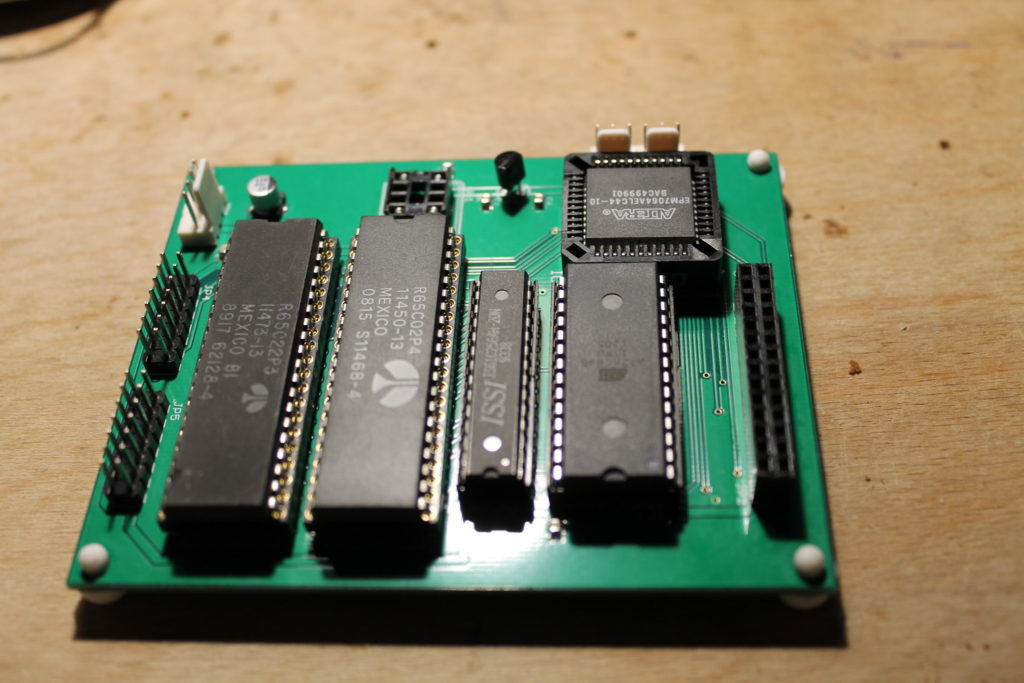

HW konfigurácia

- CPU R65C02

- VIA R65C22 = 0xD000 až DFFF nastaviteľné v CPLD

- RAM IS61C256 = 32K 0x0000 až 0x8FFF natvrdo

- EEPROM AT28C64 = 8K 0xE000 až 0xFFFF nastaviteľné v CPLD

- CPLD EPM7064 alebo EPM3064 = IRQ a MNI routing, dekódovanie adries prípadne nejaký IO obvod (4 adresy). 4 IO porty sú volné a vyvedené na header.

- Zjednodušená zbernica vyvedená na konektor. 16K rozsah CS a IRQ pin ovládaný CPLD.

Možnosti konfigurácie

- EEPROM môže byť umiestnená kdekoľvek v rozsahu 0x8yyy až 0xFyyy. Horné 4K na F/D/B/9, a dolné na E/C/A/8.

- CPLD/VIA/IOx môžu byť tiež v rozsahu 0x8 až 0xF.

- V CPLD môže okrem základnej logiky obsahovať aj ďalšiu logiku (SPI/SERIAL/IEC/…)

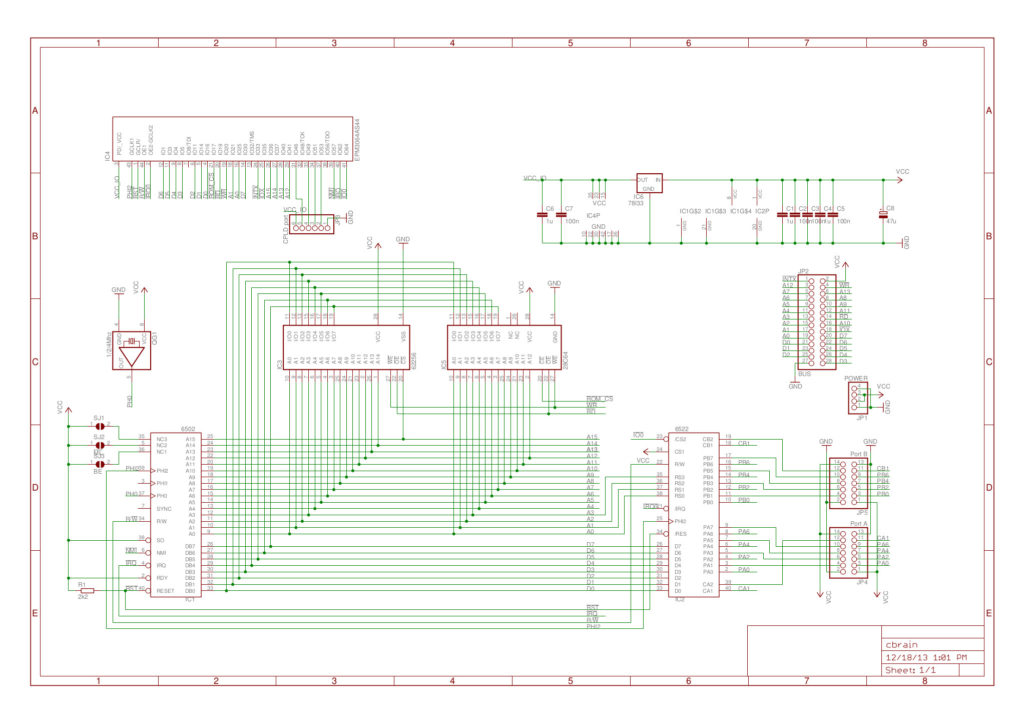

Schéma

Podklady projektu EAGLE,VHDL …. (Nejde v IE nevie tak bezpečné SSL)

Podklady projektu EAGLE,VHDL …. (Nejde v IE nevie tak bezpečné SSL)

Fotky riešenia

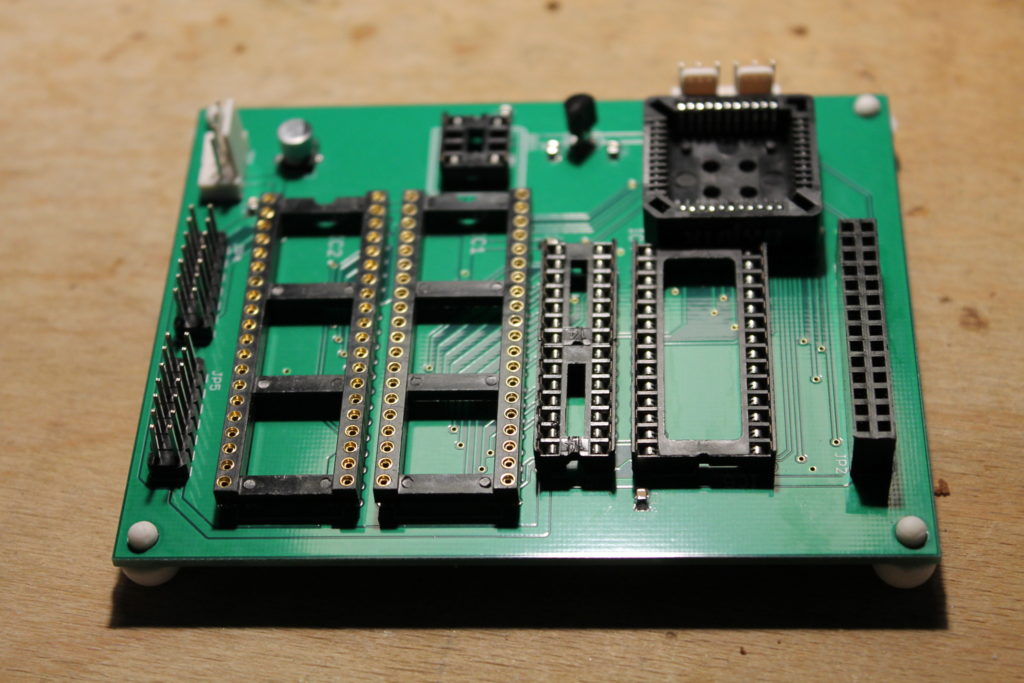

Osadené pätice a bižutéria.

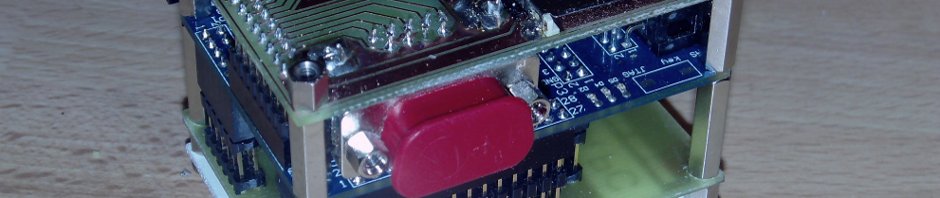

Takto to bude vyzerať keď to bude „funkčné“ a osadené. Ešte mi chýba oscilátor.

Takto to bude vyzerať keď to bude „funkčné“ a osadené. Ešte mi chýba oscilátor.

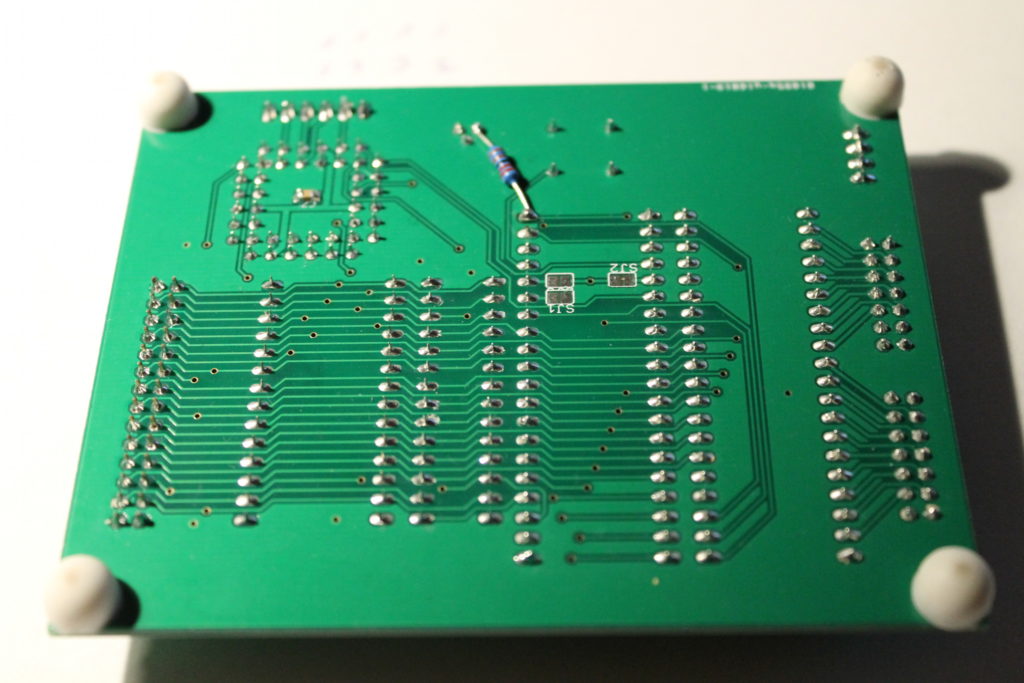

A v prvej iterácii PCB chýbal pull-up odpor pre RESET. Našťastie riešenie nieje zložité. Aktuálne eagle súbory ho už majú.

A v prvej iterácii PCB chýbal pull-up odpor pre RESET. Našťastie riešenie nieje zložité. Aktuálne eagle súbory ho už majú.