Keďže som ešte stále naladený na VHDL a moc sa mi nechce prepínať do 6502 assembleru. Ktorý sa musím viacmenej naučiť odznova, Lebo bez neho nenaprogramujem FLASH z ZZ_RAM. Som rozmýšľal nad možnosťami využiť CPLD ako alternatívu k ťažšie zohnatelnými IO. Prípadne vyrobiť si nejaký IO ktorý sa zíde a nedá sa kúpiť. Ako prvé padol nápad na SPI, Ktoré je použiteľné z C64 ale aj z mojím ďalším projektom C_BRAIN. Čo by mal byť univerzálny koprocesor pre C64 komunikujúci cez IEC.

Ale naspäť k SPI. Na internete sa dá nájsť 65SPI Ktorý je ale na môj vkus moc veľký, V mojom názore ma utvrdil aj projekt ZXMMC ktorý do rovnakého CPLD vtesnal nielen SPI ale i sériový port. A to všetko vďaka tomu že sa nezapodieval nepotrebnými zbytočnosťami. Ako sú generátory hodín či ďalšie málo využívané nastavenia.

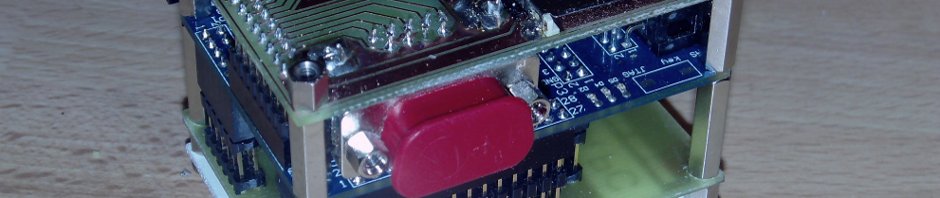

Moje pokusy z prvú tiež ukazovali na fakt ze do 32 makrobuniek sa SPI vtesnať nedá ale opak bol pravdou. Aktuálna ALFA verzia určená do VHDL replík má v MAX3000 rade len 15 makrobuniek. A to narozdiel od verzie v ZXMMC má možnosť nastavenia SPI modu. Jediné čo tu chýba je generovanie CS ale to je len obyčajný register.

Ak simulácie a reálne nasadenie ukážu že riešenie je dobré ďalší na rade bude sériový port.