C_Brain dostal novú logiku. Pôvodná verzia podporovala len adresný dekodér a generovanie nRD a nWR. Tentoraz som pridal aj podporu zamykania zápisu do EEPROM a popdoru pre MNI a IRQ.

Podpora je realizovaná pomocou dvoch registrov v rozsahu 0xC000 – 0xC003. Tie sú zrkadlené v celom rozsahu 0xC000 až 0xCFFF.

- 0xC000 – R/W Predpokladané využitie pre SPI/Sériový port. Ešte nie som rozhodnutý

- 0xC001 – R/W Nastavenie a stav SPI/Sériového portu.

- 0xC002 – RO IRQ vektor register. Obsahuje číslo prerušenia z najväčšou prioritou.

- 0x03 – IRQ0 – VIA chip

- 0x02 – INTX – Externé rozširenie

- 0x01 – spiIRQ – Prerušenie od SPI/Sériový portu.

- 0x00 – žiadne IRQ

- 0xC003 – RW Systémový register.

- D7 – LockH – Uzamknutie zápisu do hornej časti EEPROM

- 1 – Zamknuté – RESET stav

- 0 – Odomknuté

- D6 – LockL – Uzamknutie zápisu do spodnej časti EEPROM

- 1 – Zamknuté – RESET stav

- 0 – Odomknuté

- D1 a D2 – nmiSEL – Výber NMI zdroja

- 00 – Žiadne NMI – RESET stav

- 01 – spiIRQ

- 10 – INTX

- 11 – IRQ0

- D7 – LockH – Uzamknutie zápisu do hornej časti EEPROM

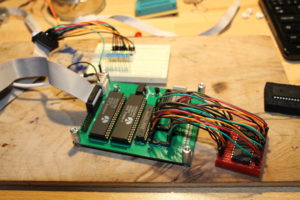

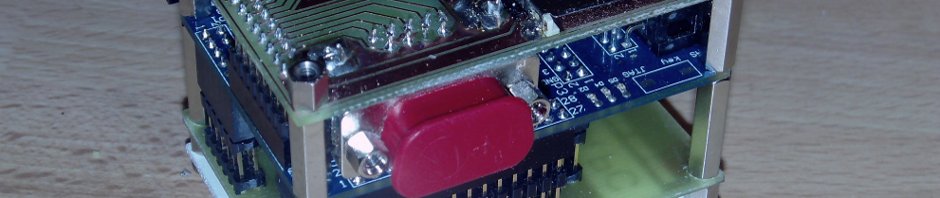

Nakoniec ešte fotka prototypu z poslednou verziou CPLD core. Testoval som len či nové jadro nemá dopad na funkčnosť.