Tak konečne som vyladil logiku C_brain-u. A už mi tam maká prvý program. Nerobí nič horibilné na portoch VIA A a B počíta on 0x00 do 0xFF a dokola. Ale konečne mi to neprepisuje EEPROM.

Programček je veľmi jednoduchý:

; CRASM code; license GPL v 3.0 ; autor: Marek Blasko cpu 6502 ; Select 6502 CPU output hex ; select output format to intelhex ; io adresses prb = $D000 ; Port register B pra = $D001 ; Port register A ddrb = $D002 ; Data direction register B ddra = $D003 ; Data direction register A t1_lo = $D004 ; Timer 1, low byte t1_hi = $D005 ; Timer 1, high byte t1l_lo = $D006 ; Timer 1 latch, low byte t1l_hi = $D007 ; Timer 1 latch, high byte t2_lo = $D008 ; Timer 2, low byte t2_hi = $D009 ; Timer 2, high byte sr = $D00A ; Shift register acr = $D00B ; Auxiliary control register pcr = $D00C ; Peripheral control register ifr = $D00D ; Interrupt flag register ier = $D00E ; Interrupt enable register pra2 = $D00F ; Port register A w/o handshake * = $E000 ; ROM start code begin lda #$FF ; nastavyme VIA porty ako vystup sta ddrb sta ddra aj lda #$00 ; vynulujeme si pocitada yj ldy #$00 xj ldx #$00 zj inx bne zj iny bne xj adc #$01 sta prb sta pra bne yj jmp aj code ; settings IRQ/RES/NMI vectors * = $FFFA NMIVEC dw begin ; Make the NMI vector point to NMI ISR if you have one. RESVEC dw begin ; Make the reset vector point to the reset routine. IRQVEC dw begin ; Make the IRQ vector point to the timer counter ISR.

Ešte malé video z výstupom programu. 7 segmentovka bola použitá preto že nemám á použiteľných LED diód.

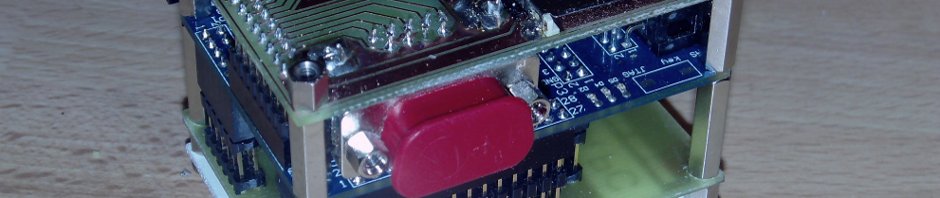

Bohužiaľ nie všetko šlo podla mojich predstáv. Jeden z CPU nejde, Na funkčnom som ulomil RESET nožičku. Našťastie dostal náhradnú amputovanú z 741P. Takže nebudem môcť vyrobiť druhý kus. Chýba mi len CPU. No čo už ďalšia verzia bude z PLCC procesormi ktoré ešte mám.

Ďalším programom bude test RAM. Aspoň sa precvičím z programovaní v assemblery A skúsim vytvoriť definície pre CC65.