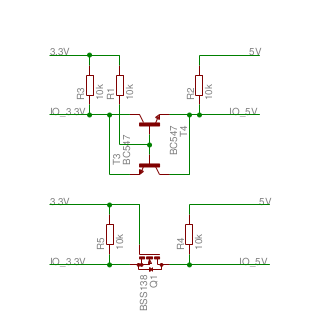

Pri riešení problému z Reset a Halt signálov medzi Akcelerátorom a amigou som našiel pekne riešenie. V prípade plánovaného FPGA akcelerátora je možným riešením oddelením signálov a výstupný a vstupný. Ale pokiaľ to nieje možné. Napríklad pri použití MC68SEC000 na 3.3V z dôvodu nižšieho zahrievania. Je tu možnosť použiť level shifter. Na obrázku sú dve možné realizácie. Pripojením báz/gates tranzistorov na logiku je možné aj riešiť rozpojenie.

3.2.1 ……

Len ďalšia WordPress stránka