Nemal som moc času na písanie a ani na koníčky ale dúfam ze sa to už napraví. Začnem teda drobnosťami ktoré som zatiaľ porobil a mohli by sa niekomu hodiť.

Archív kategorií: AVR

SBC z AVR.

Martin Maly na stránke retrochip.cz písal o tom ze by rád spravil jednodoskáč na bázy AVR. A pripomenul mi jeden môj „projekt“ na ktorý padá prach. Pokiaľ chcete ako vyzerá správny jednodoskáč tak najväčší špecialista ktorého poznám, na túto oblasť má stránku nostalcomp.cz. Dnes nájdete veľa projektov SBC (Single Board Computer) ale máloktorý je pravoverný SBC. To znamená že na prácu nepotrebujete ďalší počítač či aspoň terminál.

Ako som si zaoptimalozoval.

Na jednom projekte som sa dostal na obmedzenia veľkosti flash v ATtiny2313. Tak som sa vrhol na optimalizáciu (Kód sa kompiloval z prepínačom -Os). V kóde som našiel len jednu možnosť ako optimalizovať veľkosť. Zbaviť sa násobenia a delenia. Vo výsledku sa mi celkový kód scvrkol o 98 bytov oproti pôvodnej veľkosti.

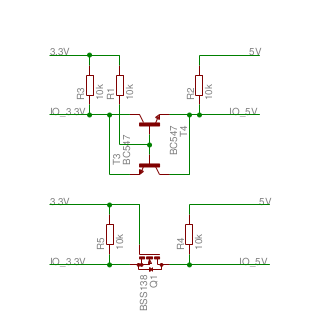

Obojsmerna komunikacia medzi 5V a 3.3V logikou

Pri riešení problému z Reset a Halt signálov medzi Akcelerátorom a amigou som našiel pekne riešenie. V prípade plánovaného FPGA akcelerátora je možným riešením oddelením signálov a výstupný a vstupný. Ale pokiaľ to nieje možné. Napríklad pri použití MC68SEC000 na 3.3V z dôvodu nižšieho zahrievania. Je tu možnosť použiť level shifter. Na obrázku sú dve možné realizácie. Pripojením báz/gates tranzistorov na logiku je možné aj riešiť rozpojenie.

USB -> I2C -> 1Wire

Keďže už mám HW,FW a aj I2C to 1wire švába bolo načase spraviť konečné riešenie.

I2C_tiny_USB na mojej verzii HW

Na testy z 1wire som potreboval I2C host adaptér. A ako jedno z naj jednoduchších riešení vychádza I2C_tiny_USB. Bohužiaľ sa mi nechcelo stavať nový HW Tak som upravil FW teraz používa interný oscilátor ktorý je pomocou PLL doladení na 16.5 MHz. Zdrojový kód i2c_tiny_usb.zip (premenujte si na .tgz)

Ako pripojit 1Wire/iButon k MCU

Pokiaľ hľadáte jednoduchú zbernicu ktorá zvládne aj väčšiu vzdialenosť. Pravdepodobne sa dostanete k 1wire. Ale ako pripojiť takéto zariadenie k MCU? Je niekoľko možností …..

Temperme.com mini a na čo sa dá použiť.

Malý prehľad možností ako temper.me mini používať.

Môže sa zdať ze 3 I/O porty sú málo ale nieje to až tak zlé. Používajú sa všetky funkcionality ktoré sú aktuálne implementované v mojom univezálnom FW. A ďalšie ktoré sa budú pridávať sa do použitých ATtiny25 už nevmestia.

Posun v projekte temperme.com (4)

Tak po stránke HW a FW je všetko hotové.

Posun v projekte temperme.com (3)

Par obrázkov a logov