Linka na knižnicu: zz_libs.lbr. Do tejto knižnice dávam všetko čo nenájdem na nete.

Archív kategorií: HW a SW

Obojsmerna komunikacia medzi 5V a 3.3V logikou

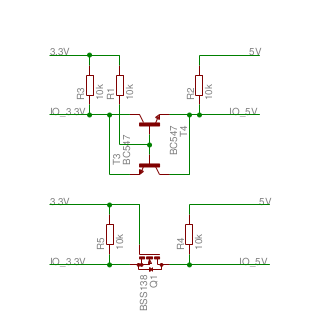

Pri riešení problému z Reset a Halt signálov medzi Akcelerátorom a amigou som našiel pekne riešenie. V prípade plánovaného FPGA akcelerátora je možným riešením oddelením signálov a výstupný a vstupný. Ale pokiaľ to nieje možné. Napríklad pri použití MC68SEC000 na 3.3V z dôvodu nižšieho zahrievania. Je tu možnosť použiť level shifter. Na obrázku sú dve možné realizácie. Pripojením báz/gates tranzistorov na logiku je možné aj riešiť rozpojenie.

USB -> I2C -> 1Wire

Keďže už mám HW,FW a aj I2C to 1wire švába bolo načase spraviť konečné riešenie.

I2C_tiny_USB na mojej verzii HW

Na testy z 1wire som potreboval I2C host adaptér. A ako jedno z naj jednoduchších riešení vychádza I2C_tiny_USB. Bohužiaľ sa mi nechcelo stavať nový HW Tak som upravil FW teraz používa interný oscilátor ktorý je pomocou PLL doladení na 16.5 MHz. Zdrojový kód i2c_tiny_usb.zip (premenujte si na .tgz)

Urobili mi radosť.

Včera som bol obdarovaný dvomi kusmi DS2482-100. Takže môžem začať z 1wire pokusmi aj mimo RaspberryPI.

Urobil som si radosť 2

Tak dnes som sa činil a spravil si radosť hneď dva krát. Druhý prípad bolo zabudovanie SCSI radiča do môjho PC. čo nieje nič svetoborného kým nespomeniem že vlastním miniITX krabicu ktorá nič takéto neumožňuje.

Urobil som si radosť 1

Tak som si spravil prenosný monitor na rôzne testovanie. Základom je LCD kontroler z Ebay a TFT LCD z mini tabletu, Pri páde prišiel o dotykovú vrstvu tak som mu hľadal využitie. Okrem dvoch kompozitných vstupov obsahuje aj VGA vstup. Kontroler všetko konvertuje do natívneho rozlíšenia LCD ,ktoré je 480×272. Vcelku zaujímavý pohľad keď pripojím VGA signál 1024×768.

Prišli pogo-piny!

Tak jedna z posledných veci co mi aktuálne chýbali ku šťastiu prišla. Pogo piny sú doma. Plánujem ich použiť na programovanie „produkčných“ akcelerátorov.

Ako pripojit 1Wire/iButon k MCU

Pokiaľ hľadáte jednoduchú zbernicu ktorá zvládne aj väčšiu vzdialenosť. Pravdepodobne sa dostanete k 1wire. Ale ako pripojiť takéto zariadenie k MCU? Je niekoľko možností …..

Trocha netradičné využitie FPGA

Hexapod Robot based on FPGA a troska jednoduchsi LEGO robot Quadroped Robot – (NIOSII Assembly)