Na fóre pre fanúšikov procesorovej rady 6502 som objavil vcelku zaujímavý projekt: CHOCHI. Jedná sa o jednoduchy FPGA board . FPGA + konfig FLASH + RAM. Nic moc ale dôležitejší je Firmware. V tomto prípade sa jedná o minimalistický 6502 počítač zo sériovým portom a IO portami. Po zapnutí očakáva zaslanie programu cez sériovú linku. Na stránke projektu je k dispozícii Monitor, Basic, Forth. Jediná vec ktorá mi vadí na projekte je že zdrojové kódy konfigurácie FPGA sú vo Verilogu. Neovládam ho.

Archív kategorií: FPGA

Minimalisticke SPI u_SPI

Keďže som ešte stále naladený na VHDL a moc sa mi nechce prepínať do 6502 assembleru. Ktorý sa musím viacmenej naučiť odznova, Lebo bez neho nenaprogramujem FLASH z ZZ_RAM. Som rozmýšľal nad možnosťami využiť CPLD ako alternatívu k ťažšie zohnatelnými IO. Prípadne vyrobiť si nejaký IO ktorý sa zíde a nedá sa kúpiť. Ako prvé padol nápad na SPI, Ktoré je použiteľné z C64 ale aj z mojím ďalším projektom C_BRAIN. Čo by mal byť univerzálny koprocesor pre C64 komunikujúci cez IEC.

Velkost roznych VHDL CPU. updated

Keďže hľadám vhodný VHDL cpu na simulovanie tape/floppy pre FPGA PC Som sa rozhodol porovnať veľkosti jednotlivých CPU dostupných z Opencores.org a iných zdrojov.

Jupiter Ace na FPGA_PC

Po par doch trápenia sa mi podarilo rozchodiť Jupiter Ace. Bohužiaľ generované video si nejak nerozumie z mojim LCD monitorom. Našťastie aspoň LCD televízor má rozum.

FPGA_PC v novej krabičke.

Tak po víkende z pilníkom a pílkou dostal FPGA_PC krabičku. A ZX81 v nom nový BackPorch generátor.

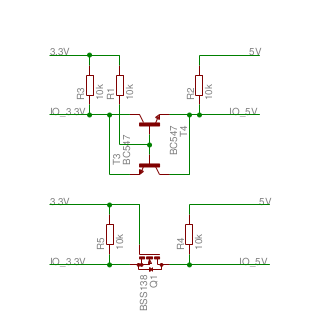

Obojsmerna komunikacia medzi 5V a 3.3V logikou

Pri riešení problému z Reset a Halt signálov medzi Akcelerátorom a amigou som našiel pekne riešenie. V prípade plánovaného FPGA akcelerátora je možným riešením oddelením signálov a výstupný a vstupný. Ale pokiaľ to nieje možné. Napríklad pri použití MC68SEC000 na 3.3V z dôvodu nižšieho zahrievania. Je tu možnosť použiť level shifter. Na obrázku sú dve možné realizácie. Pripojením báz/gates tranzistorov na logiku je možné aj riešiť rozpojenie.

Trocha netradičné využitie FPGA

Hexapod Robot based on FPGA a troska jednoduchsi LEGO robot Quadroped Robot – (NIOSII Assembly)

Zaujímavý web.

Narazil som na zaujímavý web Retro Ramblings. Jedná sa o web zaoberajúci sa FPGA a simuláciou retro počítačov na nich.

Clovdova sluzba pre vyvoj VHDL (2)

VGA monitor k 8bitom.

Pri čítaní mojej obľúbenej stránky www.8bity.cz som narazil na konštrukcie ktoré slúžia na pripojenie VGA monitorov k 8bit počítačom.