Po par doch trápenia sa mi podarilo rozchodiť Jupiter Ace. Bohužiaľ generované video si nejak nerozumie z mojim LCD monitorom. Našťastie aspoň LCD televízor má rozum.

Urobil som obchod storočia!!

Vymenil som Apple Pro G5, ktoré mi tu zavadzalo za ……..

FPGA_PC v novej krabičke.

Tak po víkende z pilníkom a pílkou dostal FPGA_PC krabičku. A ZX81 v nom nový BackPorch generátor.

Raspberry PI v Eagle knižnici

Linka na knižnicu: zz_libs.lbr. Do tejto knižnice dávam všetko čo nenájdem na nete.

Amigapoint 2013

Po vyše týždni par fotiek z tejto akcie. Ono osobne nie som „správny amigista“. Takže som si vystačil z pol dňovou návštevou tejto akcie.

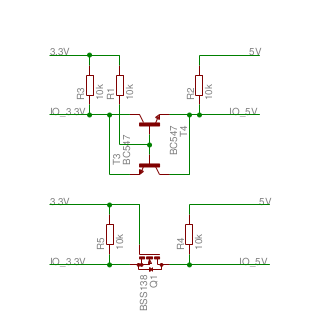

Obojsmerna komunikacia medzi 5V a 3.3V logikou

Pri riešení problému z Reset a Halt signálov medzi Akcelerátorom a amigou som našiel pekne riešenie. V prípade plánovaného FPGA akcelerátora je možným riešením oddelením signálov a výstupný a vstupný. Ale pokiaľ to nieje možné. Napríklad pri použití MC68SEC000 na 3.3V z dôvodu nižšieho zahrievania. Je tu možnosť použiť level shifter. Na obrázku sú dve možné realizácie. Pripojením báz/gates tranzistorov na logiku je možné aj riešiť rozpojenie.

Moja testovacia Amiga 600 dostala novy podvozok ;-)

Moja testovacia Amiga trpela pod bordelom na stole. Čo viedlo sem tam k nevysvetliteľnému správaniu. Nakoniec to vyriešilo par minút z vŕtačkou a plastová doska na krájanie.

ICOO T55 a úprava na funkčné OTG

Potom čo som otvoril môj Mini Pad JXD S18. Je čas aj na starší kúsok Icoo T55. Jedná sa o android z MIPS2 CPU, čo je vcelku vzácnosť. Má ešte dva „klony“ Gemei HD8900 a HD8900 PRO. Gemei verzie majú na dve rozšírenia, funkčné OTG USB a kompozitný video výstup. Ako rozchodiť OTG som už prišiel. a na konci článku ho aj ponúkam.

Tak na amigaportal.cz fóru ma už nik neuvidí.

Jak to vypadá keď si admin fóra mení spravu z liečeným komplexov? Uvidíte na fóre amigaportálu. Teda neuvidíte, lebo kto maže ten jede.