Po dlhšom čase som zas naštartoval moju virtuálnu serverovňu a rozhodol sa že ju prerobím na aktuálne verzie z menšími zmenami.

Čo sa zmenilo a zmení:

Po dlhšom čase som zas naštartoval moju virtuálnu serverovňu a rozhodol sa že ju prerobím na aktuálne verzie z menšími zmenami.

Čo sa zmenilo a zmení:

Keď sa práve nesnažím dostať do formy po zimnom „spánku“ vozím sa na mojej novej motorke. A z jedného takéhoto výletu som si doniesol CB staničku TEAM TS-404. Je stará, bez mikrofónu ale jak sa vraví darovanému koňovi na zuby nepozeraj.

Na oldcomp fóre sme riešili náhradné riešenie napájania pre C64. Povodní zdroj generuje +5V ale aj izolovaných ~9V. Existujú tri možné riešenia ako to zrealizovať.

Nemal som moc času na písanie a ani na koníčky ale dúfam ze sa to už napraví. Začnem teda drobnosťami ktoré som zatiaľ porobil a mohli by sa niekomu hodiť.

Písať nejaký program na PMI-80 je pôrod ale keď človek nemá popis kláves je to čistý masochizmus. Preto som sa konečne rozhýbal a nejakú spravil.

Na Ebay som si kúpil lacný spektrálny analyzátor a generátor 138Mhz až 4.4Ghz (existuje aj verzia ktora ide od 35Mhz). Toto zariadenie má RF výstup obdĺžnikového priebehu a vstup analyzátoru osadený mixérom a logaritmickým detektorom. A pomocou programu LinNWT/WinNWT je toto zariadenie plnohodnotné. A je možne ho použiť ako generátor relatívne presnej frekvencie (~-7dBm) a spektrálny analyzátor (-75dBm až 17dBm). Za pomoci šumového generátora je možné merať aj filtre ci antény. (Lokálna kópia dokumentu)

Pri doplnení flash pamäte K SOCZ80 som narazil na zaujímavy problém. Aj keď pamäte poznajú rovnaké príkazy nemusia ich rovnako realizovať. V mojom prípade je problematický „Page program 0x02“. Ktorý niektoré pamäte realizujú ako zápis jedného Bytu. Iné ako sekvenčný zápis bez obmedzenia veľkosti a ďalšie len z obmedzením na 256. Prikladám tabuľku z môjho čítania datashetou. Vybral som len príkazy ktoré sú „použiteľné“ v bežnej praxi.

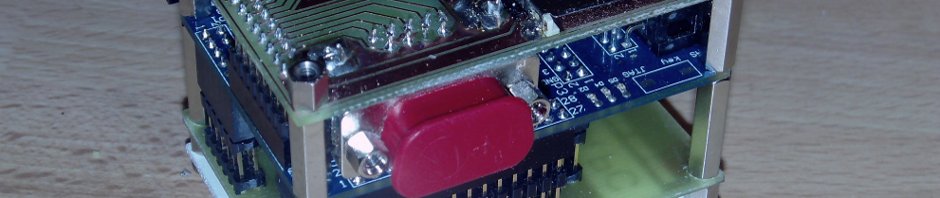

Pozeral som ako minúť moje ďalšie staré FPGA kity a narazil som na SOCZ80. Jedná sa o extrémny stroj z 8M SDRAM, Serial Flash, SD a dvoma sériovými portami. Povodní je pre Xilinx ale existuje aj úprava na Altera. Pôvodná verzia na xilinxe beží na 128Mhz, Altera verzia beží len 50Mhz. Mnou používané FPGA sú dosť malé, preto bol vyhodený kód pre cache, preto je CPU brzdené.

na stranke projektu som pridal link na zdrojaky projektu